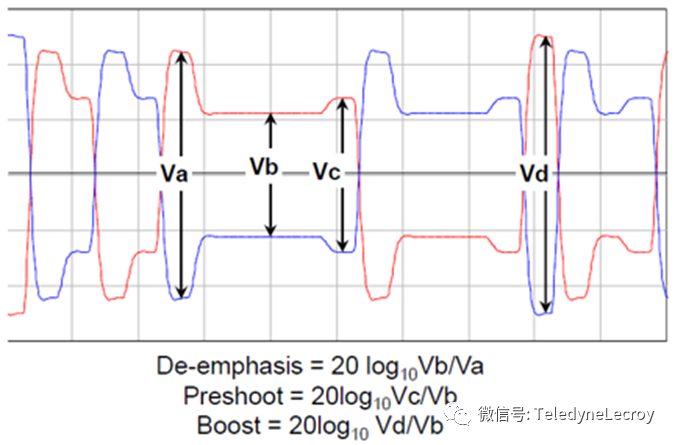

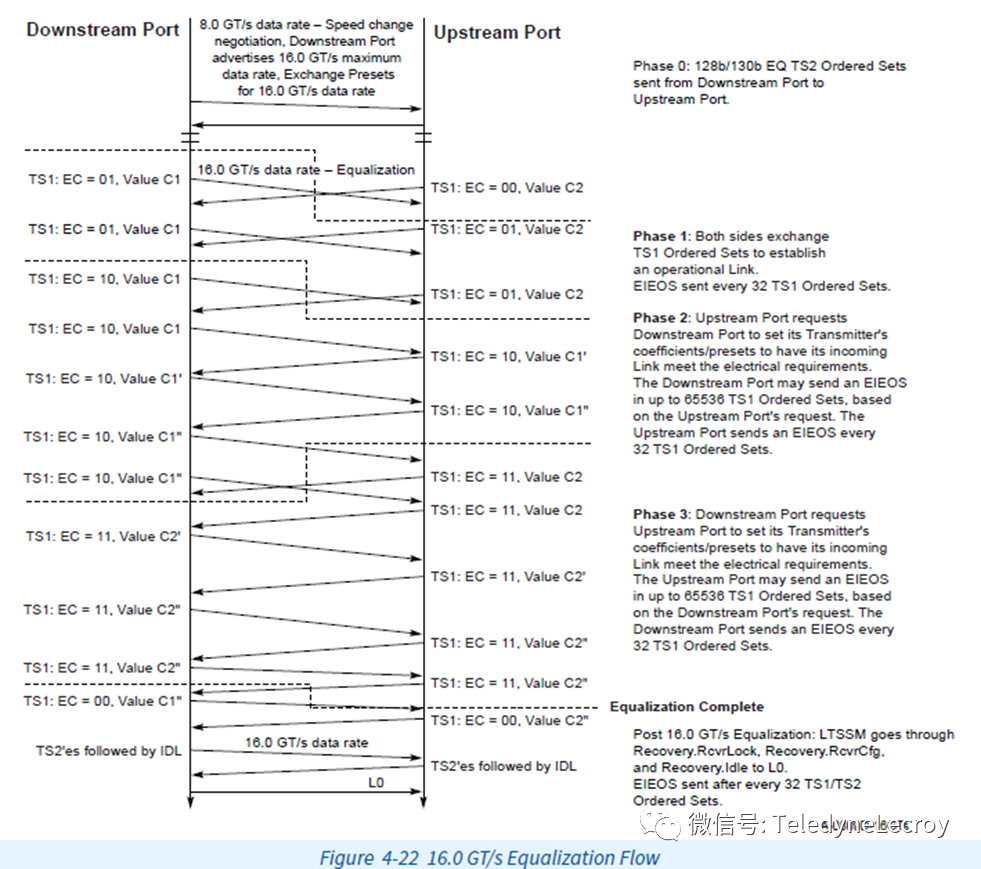

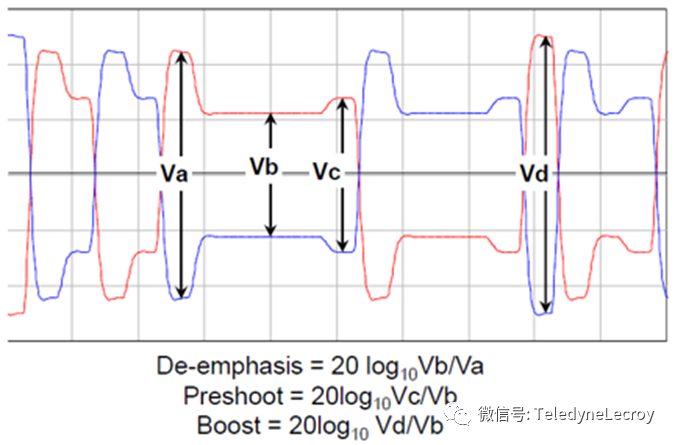

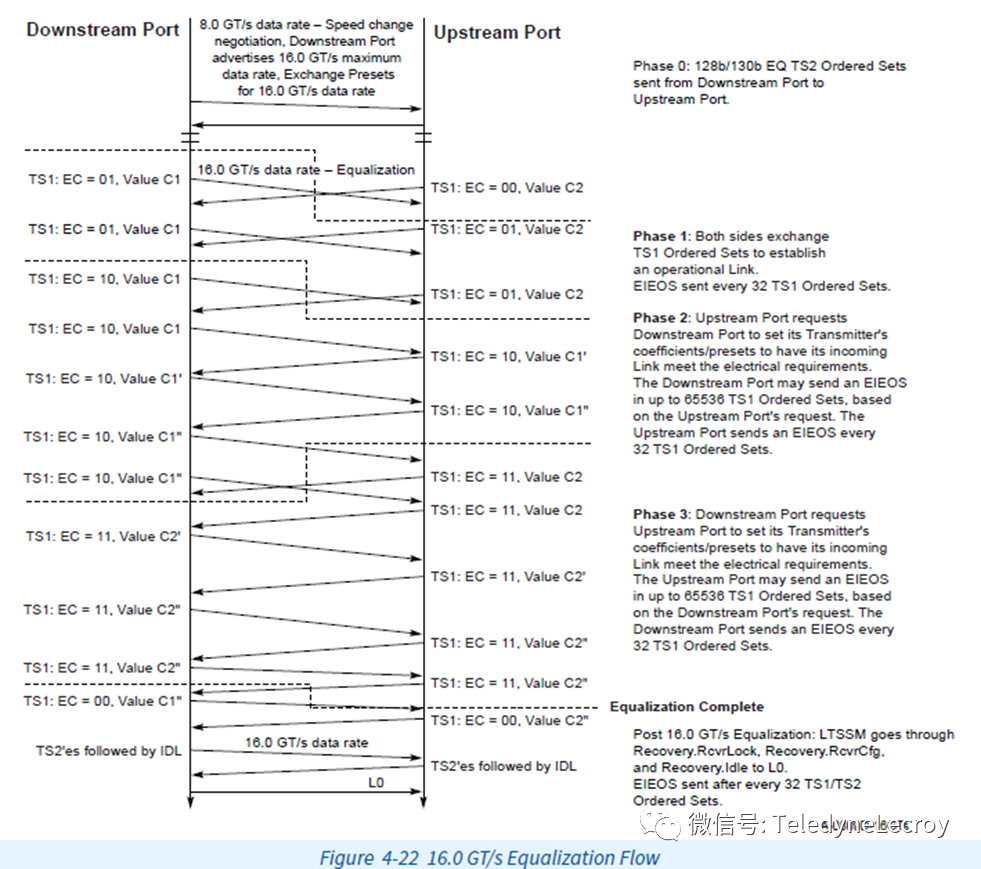

随着连续几代 力科PCIe协议分析仪 Express 以 8 Gbps、16 Gbps 和 32 Gbps 的速度运行,动态链路均衡变得至关重要。均衡会补偿通信信道对信号的影响。这些影响包括充当低通滤波器的链路,它会衰减数据流中的关键高频分量,此外,由连接器和过孔引起的链路阻抗不连续会进一步降低链路性能。PCIe协议分析仪均衡可应用于发送端 (TxEQ)、接收端 (RxEQ) 或两端都应用, TxEQ 涉及去加重和预冲,而 RxEQ 涉及连续时间线性均衡 (CTLE) 和判决反馈均衡 (DFE)。在发送端,去加重会使跳变后的第一位以全幅度 (Va) 发送,相同极性的后续位以降低的电平 (Vb) 传输,但在下一次跳变之前的最后一位除外,它以提高的预冲电平 (Vc) 传输。此外,转换之间的单个bit位以最大增强电平 (Vd) 传输。去加重和增强的组合补偿了链路会衰减的信号高频成分。均衡涉及多个阶段的链路训练序列,有时会产生意想不到的结果。 使用 PCIe协议分析仪 CrossSync PHY关联协议层和物理层数据的能力可以帮助定位链路训练后可能出现的逻辑和电气问题。发送端均衡(去加重、预冲和增强),是由 PCIe 系统的 TxEQ内的三抽头有限脉冲响应 (FIR) 滤波器实现。链路训练的目标是确定给定通信链路的最佳 FIR 滤波器系数,也称为游标系数。链路训练在下行端口和上行端口之间交换有序数据集,包括TS1训练序列和TS2训练序列 。以PCIe4.0协议分析仪为例,PCIe 4.0 链路训练从速度变化协商开始,有4个阶段,阶段 0 到阶段 3。在阶段 0,下行端口以 8GT/s 数据速率向上行端口发送 TS2 有序集,通告 16GT/s 的最大数据速率。在阶段 1,两个端口交换 TS1 有序集,在每 32 个 TS1 有序集之后穿插一个电气空闲退出有序集 (EIEOS),以建立操作链路。EIEOS 的目的是保证链路伙伴可以检测到电气空闲退出状态,EIEOS 数据包符号(四个交替的 00 00 FF FF 序列)产生规则且具有相对较少的转换的电信号,这对于在调试期间观察信号的物理层属性非常有用。