8b10b编码基础-云帆兴烨

8b/10b编码的应用非常广泛,例如:PCIE GEN1 GEN2,USB3.2 GEN1。再到现在的128b/130b (PCIE GEN3/4/5) 128b/132b (USB3.2 GEN2), 与8b/10b相比他们提升了编码效率,这两种编码方式在底层逻辑上和处理的问题其实是相同的,本文从什么是8b/10b编码、为什么要使用8b/10b编码和如何实现8b/10b编码三个方面来给大家介绍这项技术。

1

什么是 8b/10b 编码

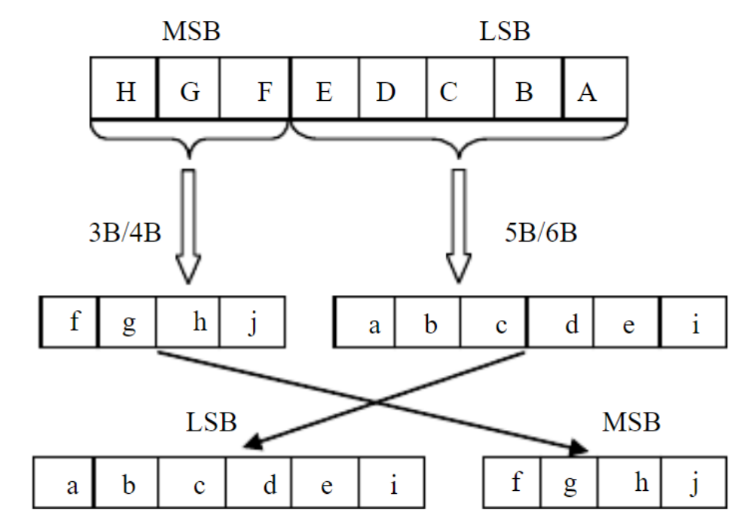

8b/10b就是把8个bit的数据加工映射成10个bit。如图1所示,我们可以看到会把8个连续的bit分成低5位 (LSB) 和高3位 (MSB) 分别进行映射,5位通过5b/6b编码,3位通过3b/4b编码。

图1 8b/10b编码映射图

2

为什么要进行 8b/10b 编码

那么为什么要把8个bit编码成10个bit?为什么要浪费两个bit,不去传输有用数据?原因有以下两点:

可以用多出来的bit位来传输一些控制信息

可以通过这种方式来达到直流均衡

公式1

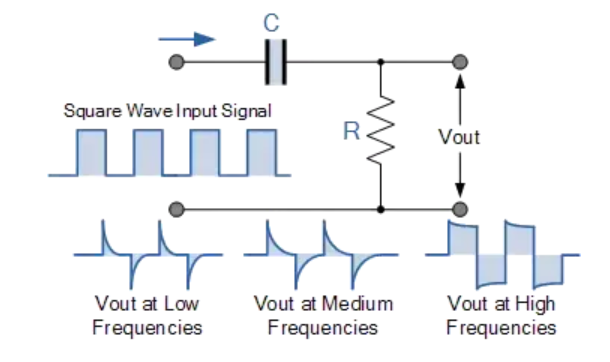

图2 不同频率的NRZ码型通过电容

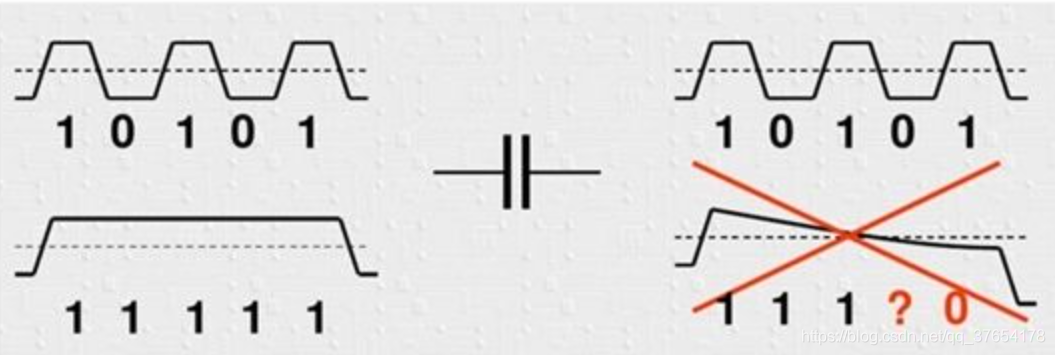

当数据位流中出现多个连续的1或0时,可以认为该时间段信号是直流的,电容的损耗变大,导致信号的幅度降低,直流信号被滤除,到最后无法识别是1还是0。且接收端收到连续的1或0时,没有充分的定时信息,给接收端的解码带来了困难(见图3)。

图3 连1连0信号通过电容信号失真

因此,8b/10b编码就是把信号中的连1连0通过多加两位的冗余,来实现映射后的信号尽量是01交替的情况,换一种说法,就是映射后的信号中尽量有相同数量的0和1。下面我们就来看一下8b/10b编码具体是怎么把8bit映射成10bit的。

3

如何实现 8b/10b 编码

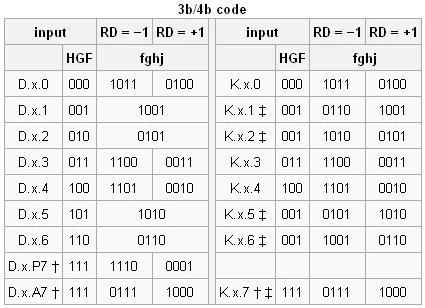

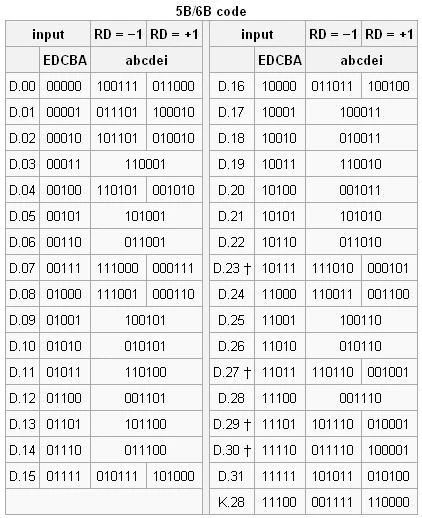

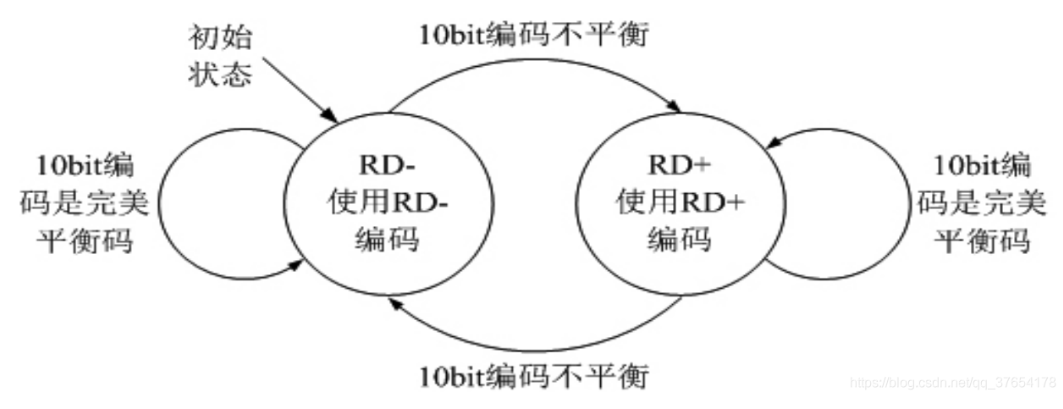

表1和表2就分别是3b/4b和5b/6b的映射关系表,通过映射后的数据是不会出现全1或者全0的。可以看到一个码型能被编码映射成多个码型而且又分为RD+和RD-,这又为什么?

表1 3b/4b编码映射表

表2 5b/6b编码映射表

图4 8b/10b编码状态转移图

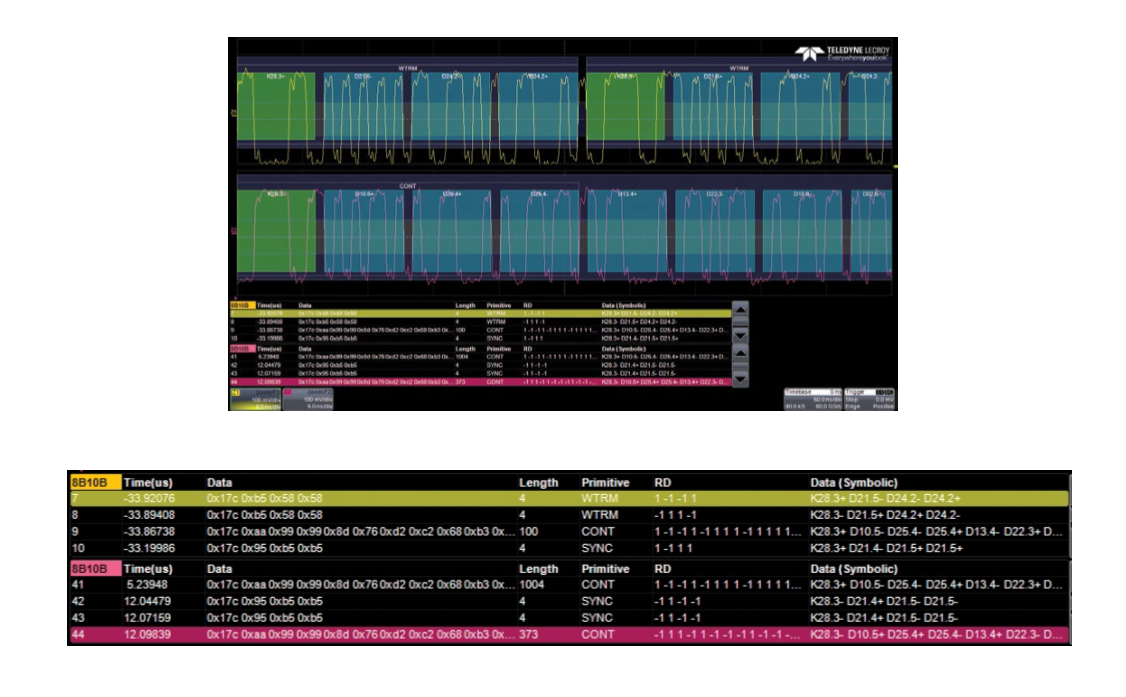

解码8b/10b串行数据波形并且会在波形上进行细致的注释,协助工程师排查问题

关联协议事件到物理波形更深入的洞察;将数据保存到磁盘方便后续进一步分析

支持多通道操作,可同时查看多达四个通道

协议解码能力高达 16 Gb/s

特励达力科的8b/10b解码功能强大,可以协助工程师以最简便的操作、最详尽的细节来排查问题调试串行数据中存在的问题。

图5 8b/10b解码选件实测图