高速互联损耗之导体损耗-华普通用

高速互联损耗是造成信号完整性问题的主要原因,损耗一般由四部分组成:损耗(导体损耗和介质损耗)、反射、串扰和差分传输中的模式转换。铜导体损耗是互连损耗中的一种,本文主要来分析导体损耗的影响因素。

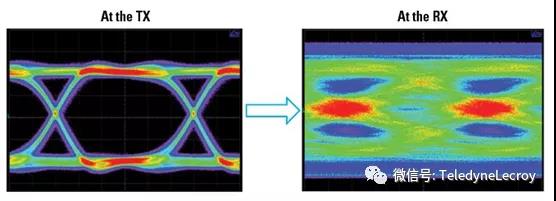

所有以1 Gbps及更高速率运行的高速电子产品都受到互连中与频率有关的损耗的影响。如果不考虑这些因素,很可能您的产品无法正常工作。这些与频率有关的损耗会将发送端的漂亮眼图变成接收端的完全闭合的眼图。

设计经济高效的系统是所需性能与功耗、成本、风险和时间成本之间的微妙平衡。尽管采用均衡可以协助眼图张开,但这是以更高的功耗为代价的。

在损耗占主导的系统中,系统的性能受到基本的物理限制,当设计受到损耗的限制时,要考虑所有可用选项,以降低系统的损耗。通常,只有两种选择:较低的耗散因子Df的板材和与理想铜性能尽可能接近的铜箔。

这些市场力量一直在驱动PCB供应商提供具有越来越低耗散因子的板材,相同的力量推动铜箔供应商,正在开发性能几乎与理想铜相同的铜箔。

铜导线每单位长度串联电阻的频率依赖性取决于三个因素:

铜电导率

线宽

表面光滑度

趋肤效应

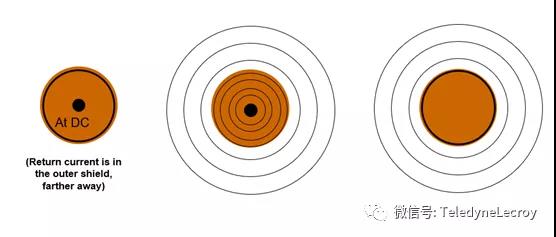

影响铜损的频率依赖性的首要因素是趋肤效应,随着频率的提高,这会导致电流在信号路径和返回路径中重新分布,意味着电流流经的横截面变小,阻抗变大。

我们可以阻抗的角度分析趋肤效应,趋肤效应可以认为是电流寻求最低阻抗路径的趋势造成的。

在DC时, 阻抗主要由电阻性阻抗决定,导体内部和外部的阻抗是一样的,电流均匀分布在导体横截面上,各处的电流密度都是一样的,

但是当输入交流信号时, 路径阻抗主要由回路电感决定,导体内部路径的电感更大,感性阻抗越大,为寻找回路电感最低路径,电流在导线上的分布会趋向导体的表面。

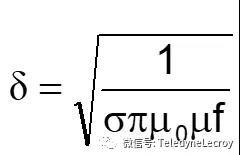

趋肤深度可以通过下面的公式来计算,串联电阻和频率的平方根成正比。

铜箔表面光滑度的影响

长期以来,我们认为表面有纹理或粗糙的铜会增加额外的损耗,最近推出的SI-VSP(非常光滑)铜箔,可能已经是铜光滑的极限。

在大约3 GHz以上,增加的铜导线串联电阻,比仅依据趋肤效应预期的要多。这与铜的粗糙度有关,在较高的频率下,表面粗糙的铜可比理想的光滑铜所预期的损耗多一倍。

铜箔生产的目标是开发一种经济高效的方法,使铜足够光滑,不会增加额外的损耗,但仍与PCB化学相容,以提供足够的附着力、机械性能和蚀刻质量

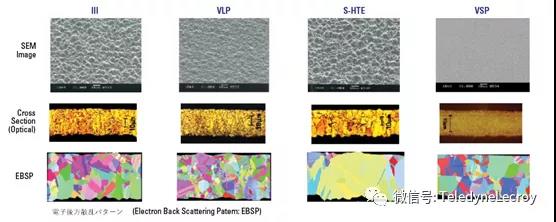

最近发布的SI-VSP铜箔,已接近理想的光滑铜性能,下图是其电沉积(ED)铜箔的镜面光滑表面纹理与其他传统ED工艺中的哑光表面处理相比的示例。

这项创新是通过新的电镀化学和工艺来设计电沉积铜箔的晶粒结构的结果。

SI-VSP铜箔成本最高,但表面也最平滑,损耗也最低。VSP铝箔的第一个版本于2012年推出。在过去的七年中,VSP铜箔的化学技术取得了进步, SI-VSP的表面轮廓均方根(Rz)约为0.5微米。

下图显示了不同等级VSP铜箔的不同结节结构和所产生的表面纹理对损耗的影响。

铜表面越光滑,损耗越小,直接的结果是,降低了电路板表面的机械粘附力。 为了补充机械附着力,箔纸出厂前已进行了三种表面处理。

进行结节处理以增加与表面的粘合,然后,将铬酸锌合金镀在铜的表面上,这样可提供化学活性更高的表面,以实现更好的附着力,但不会改变表面纹理。然后,将充当粘合促进剂的硅烷偶联剂涂覆在表面上。这些为不同的电路板化学材料定制的材料,将与电路板的粘合力提高到至少3 lb/ in的强度,它们还有助于电路板制造过程中光致抗蚀剂的附着。

硅烷偶联增粘剂既有助于与层压材料的粘合,又有助于电路板制造中光致抗蚀剂的粘合。这意味着可以更好地控制线宽,并且在需要时可以蚀刻更细的线。

不同等级的VSP铜箔都具有不同的表面纹理,对应不同的粗糙损耗以及不同的成本。当选择可接受的低损耗的最低成本箔片时,这可以在成本-性能折衷之间实现更好的平衡。这也是为什么精确的建模工具不仅对探索互连结构的性能,而且对性价比之间的平衡至关重要的另一个原因。

总结

随着新的SI-VSP铜箔的推出,铜损已达到极限。减少铜损的唯一方向就是增加线宽。在迈向更高数据速率的过程中,这将成为成本性能权衡的重要因素.